## MEMORY OPTIMIZATIONS OF EMBEDDED APPLICATIONS FOR ENERGY EFFICIENCY

## A DISSERTATION SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

Jongsoo Park May 2011 © 2011 by Jong Soo Park. All Rights Reserved. Re-distributed by Stanford University under license with the author.

This work is licensed under a Creative Commons Attribution-Noncommercial 3.0 United States License. http://creativecommons.org/licenses/by-nc/3.0/us/

This dissertation is online at: http://purl.stanford.edu/qw764dr9610

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

#### William Dally, Primary Adviser

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

#### Monica Lam, Co-Adviser

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

#### **Christoforos Kozyrakis**

Approved for the Stanford University Committee on Graduate Studies.

### Patricia J. Gumport, Vice Provost Graduate Education

This signature page was generated electronically upon submission of this dissertation in electronic format. An original signed hard copy of the signature page is on file in University Archives.

## Abstract

The current embedded processors often do not satisfy increasingly demanding computation requirements of embedded applications within acceptable energy efficiency, whereas application-specific integrated circuits require excessive design costs. In the Stanford Elm project, it was identified that instruction and data delivery, not computation, dominate the energy consumption of embedded processors. Consequently, the energy efficiency of delivering instructions and data must be sufficiently improved to close the efficiency gap between application-specific integrated circuits and programmable embedded processors.

This dissertation demonstrates that the compiler and run-time system can play a crucial role in improving the energy efficiency of delivering instructions and data. Regarding instruction delivery, I present a compiler algorithm that manages L0 instruction scratch-pad memories that reside between processor cores and L1 caches. Despite the lack of tags, the scratch-pad memories with our algorithm can achieve lower miss rates than caches with the same capacities, saving significant instruction delivery energy.

Regarding data delivery, I present methods that minimize memory-space requirements for parallelizing stream applications, applications that are commonly found in the embedded domain. When stream applications are parallelized in pipelining, large enough buffers are required between pipeline stages to sustain the throughput (e.g., double buffering). For static stream applications where production and consumption rates of stages are close to compile-time constants, a compiler analysis is presented, which computes the minimum buffer capacity that maximizes the throughput. Based on this analysis, a new static streamscheduling algorithm is developed, which yields considerable speed-up and data delivery energy saving compared to a previous algorithm. For dynamic stream applications, I present a dynamically-sized array-based queue design that achieves speed-up and data delivery energy saving compared to a linked-list based queue design.

## Acknowledgement

First and foremost, I would like to thank my advisor, Professor William Dally. Bill is an amazing person at many moments — at ski slopes or when presenting a deep insight in front of a large audience. Among his many amazing respects, what I appreciate most is his consistent optimism and belief in students' ability to solve important problems. When we do research, things do not work as we expected most of the time. I realized that an important virtue to overcome such challenging times is not being disappointed too easily and believing in solving the problem eventually. He is also a very dedicated teacher and research advisor. He had held weekly one-to-one meetings even during his leave of absence for the chief scientist position at NVIDIA. During six years (from the very first my school week at Stanford when I first met with Bill to the final meetings for comments on this dissertation), he has been amazingly consistent at carefully listening students' concern. His deep, broad insights and hard working has raised the bar for assessing my own work, which I believe one of the most valuable lessons I have learned during my PhD.

I would also like to thank my committee members, Professor Monica Lam and Professor Christos Kozyrakis. I was fortunate enough to had an opportunity to be a TA of one of Professor Lam's classes, where I have learned valuable lessons from interacting with her, particularly from her passion on teaching and research. I am also very glad to had a chance to take Professor Kozyrakis's architecture classes, which provided solid background on my research.

The CVA group is a unique environment, where students are working on verticallydiverse fields (i.e., from circuits to software). Not only have my peer students taught me valuable technical insights, but also they have been considerate while I was learning how to communicate well with colleagues in Western cultures. I found that the CVA group is one of the best research groups in Stanford EE in terms of friendly interactions including ski trips. It was also a precious experience to work in a project with many people. I would like to thank James Balfour and David Black-Schaffer, who are the founding members of the Elm project and have helped me in many respects throughout the project. Christine Avanessians, Clinton Buie, Jooseong Kim, and Youngsik Kim helped me on the programming system of the Elk project. I would also like to thank James Chen, who has shared the office with me for several years. Although he had many struggles with companies for taping out his chips, he has maintained an incredibly optimistic attitude, which has helped me to stay positive as well. There were occasional lunches at Ike's place with James Chen, Curtis Harting, and Ted Jiang. Although Ike's place is notorious for long lines, I really enjoyed joyful lunches with delicious sandwiches. I would like to thank former CVA members -Jung-Ho Ahn, Patrick Chiang, Abhishek Das, Mattan Erez, Paul Hartke, John Kim, Tim Knight, Jiyoung Park, and Manman Ren — who had kindly guided me through my earlier years. I also would like to thank other current CVA members — Daniel Becker, George Michelogiannakis, Milad Mohammadi, and Vishal Parikh — who have made my life as a CVA member enjoyable and made myself proud of being a CVA-er.

When people think of the Bay Area, the first thing coming up in their mind is usually nice weather and beautiful scenary. I was fortunate enough to enjoy not only the nice environment but also valuable interaction with many good friends. I cannot appreciate enough that I can talk face-to-face anytime with my friends whom I have known for more than 10 years even in a place far from my home country. Particularly, I thank Yeul and Eunsun for their help on settling down when I first came to Stanford, and Taehoon and Wanki for making a great year while we were roommates.

I also deeply appreciate the friendship with Marianne. We started knowing each other through the English-in-Action program but became friends, and she gave me many precious advices. Doing a PhD is a long-haul journey like marathon, and a person told me that everybody develops at least one hobby during the course. Occasional excursions to beautiful hiking trails in the Sierra Nevada has helped me to be periodically refreshed and maintain a healthy life as a graduate student. I thank Marianne for introducing those places so that I can enjoy the beauty of nature. I also thank Seokchang for teaching me photography and going to campings with me so that I can experience the nature closely. I have enjoyed running the Campus Drive with Kahye, and I hope that we can successfully finish a hiking to the Mountain Whitney and a half marathon scheduled on this July. Woongki Baek was my first roommate with whom I took many classes and studied for Quals together. With Jiwon Seo, I continued our friendship from our college robotics club and discussed many research ideas.

I would like to thank financial support from the Samsung Scholarship, the Semiconductor Research Corporation under Grant 2007-HJ-1591, and the National Science Foundation under Grant CNS-0719844. Evelin Sullivan and Claude Reichard have provided me valuable feedback on my writings including this dissertation. Professor Jaejin Lee at Seoul National University gave me an opportunity to experience compiler research before I came to Stanford.

Last but not least, I would like to thank my family. Without them, I would not be able to come to Stanford. I cannot give enough thanks to my wife, Hyejun. My time at Stanford is full of happy memories, and many of them are from Hyejun. While writing this acknowledgement, I realized multiple times that how lucky I have been at Stanford to meet such great people, and I hope this can express at least a part of my gratitude to them.

## Contents

| Abstract |                                              |                                                          |    |  |  |

|----------|----------------------------------------------|----------------------------------------------------------|----|--|--|

| A        | cknov                                        | wledgement                                               | v  |  |  |

| 1        | Introduction                                 |                                                          |    |  |  |

|          | 1.1                                          | Motivation                                               | 1  |  |  |

|          | 1.2                                          | Contributions                                            | 5  |  |  |

|          | 1.3                                          | Collaboration                                            | 8  |  |  |

|          | 1.4                                          | Organization                                             | 8  |  |  |

| <b>2</b> | 2 The Elm Project and Its Programming System |                                                          | 10 |  |  |

|          | 2.1                                          | Elm Architecture Overview                                | 11 |  |  |

|          |                                              | 2.1.1 System-level Architecture                          | 11 |  |  |

|          |                                              | 2.1.2 Micro-architecture                                 | 15 |  |  |

|          | 2.2                                          | Elm Programming System                                   | 18 |  |  |

|          |                                              | 2.2.1 Low-level Compiler Back-end                        | 19 |  |  |

|          |                                              | 2.2.2 High-level Parallelizing Stream Programming System | 19 |  |  |

|          | 2.3                                          | Chapter Summary                                          | 30 |  |  |

| 3        | Instruction Scratch-pad Memory               |                                                          |    |  |  |

|          | 3.1                                          | Overview                                                 | 32 |  |  |

|          | 3.2                                          | Related Work                                             | 34 |  |  |

|          |                                              | 3.2.1 Dynamic Instruction Placement of SPMs              | 34 |  |  |

|          |                                              | 3.2.2 Loop Caches                                        | 39 |  |  |

|   |     | 3.2.3                                                | Tagless Hit Caches    40                                                                                                           |  |  |

|---|-----|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|

|   | 3.3 | Analytic Comparison of Miss Rates of SPMs and Caches |                                                                                                                                    |  |  |

|   | 3.4 | Algori                                               | ithm $\ldots$ $\ldots$ $\ldots$ $\ldots$ $44$                                                                                      |  |  |

|   |     | 3.4.1                                                | $Pre-processing \dots \dots$ |  |  |

|   |     | 3.4.2                                                | Instruction Placement                                                                                                              |  |  |

|   |     | 3.4.3                                                | Copy and Jump Insertion                                                                                                            |  |  |

|   |     | 3.4.4                                                | Optimality for Single-level Loops                                                                                                  |  |  |

|   | 3.5 | Evalu                                                | ation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $51$                                                                            |  |  |

|   |     | 3.5.1                                                | Experimental Setup                                                                                                                 |  |  |

|   |     | 3.5.2                                                | L1 Cache Access                                                                                                                    |  |  |

|   |     | 3.5.3                                                | Energy Consumption                                                                                                                 |  |  |

|   |     | 3.5.4                                                | Execution Time and Code Size                                                                                                       |  |  |

|   | 3.6 | Discus                                               | ssion $\ldots$                                    |  |  |

|   |     | 3.6.1                                                | Sensitivity on L1 vs L0 Read Energy Ratio                                                                                          |  |  |

|   |     | 3.6.2                                                | Effectiveness of Bypassing                                                                                                         |  |  |

|   |     | 3.6.3                                                | Interaction with Other Architectural Features                                                                                      |  |  |

|   | 3.7 | Chapt                                                | ter Summary                                                                                                                        |  |  |

| 4 | Buf | fers in                                              | Static Stream Applications 66                                                                                                      |  |  |

|   | 4.1 | Overv                                                | riew                                                                                                                               |  |  |

|   | 4.2 | Queue                                                | e Capacity Computation Algorithm                                                                                                   |  |  |

|   | 4.3 | Team                                                 | Scheduling                                                                                                                         |  |  |

|   |     | 4.3.1                                                | Team Formation                                                                                                                     |  |  |

|   |     | 4.3.2                                                | Amortization                                                                                                                       |  |  |

|   |     | 4.3.3                                                | Time Complexity    86                                                                                                              |  |  |

|   | 4.4 |                                                      | ation                                                                                                                              |  |  |

|   |     | 4.4.1                                                | Experimental Setup                                                                                                                 |  |  |

|   |     | 4.4.2                                                | Buffer Space Limited Experiment                                                                                                    |  |  |

|   |     | 4.4.3                                                | Amortization Factor Limited Experiment                                                                                             |  |  |

|   |     | 4.4.4                                                | Discussion: Sensitivity to Architectural Parameters 96                                                                             |  |  |

|   | 4.5 | Relate                                               | ed Work                                                                                                                            |  |  |

|   |     |                                                      |                                                                                                                                    |  |  |

|                  |            | 4.5.1   | SDF Scheduling for Single-core Architectures | 97  |

|------------------|------------|---------|----------------------------------------------|-----|

|                  |            | 4.5.2   | SDF Scheduling for Multi-core Architectures  | 99  |

|                  |            | 4.5.3   | Loop Transformations                         | 101 |

|                  | 4.6        | Chapt   | ter Summary                                  | 104 |

| <b>5</b>         | Buf        | fers in | Dynamic Stream Applications                  | 106 |

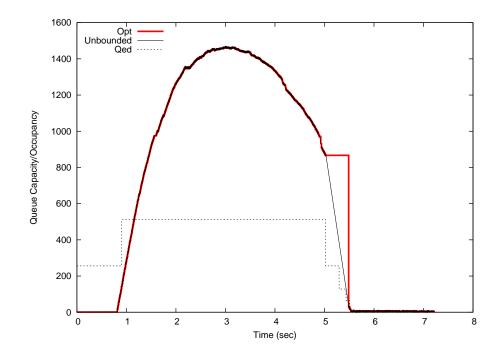

|                  | 5.1        | Overv   | iew                                          | 107 |

|                  | 5.2        | QED     | (Queue Enhanced with Dynamic sizing)         | 109 |

|                  |            | 5.2.1   | Capacity Adjustment                          | 109 |

|                  |            | 5.2.2   | Reserve-commit Interface                     | 112 |

|                  |            | 5.2.3   | Non-blocking Implementation                  | 113 |

|                  | 5.3        | Alterr  | native Methods                               | 118 |

|                  |            | 5.3.1   | Static Optimum Approximation                 | 118 |

|                  |            | 5.3.2   | Dynamic, Local Optimum Approximation         | 122 |

|                  |            | 5.3.3   | Analytical Estimation                        | 125 |

|                  | 5.4        | Exper   | imental Setup                                | 128 |

|                  | 5.5        | Evalu   | ation                                        | 132 |

|                  |            | 5.5.1   | Execution Time                               | 132 |

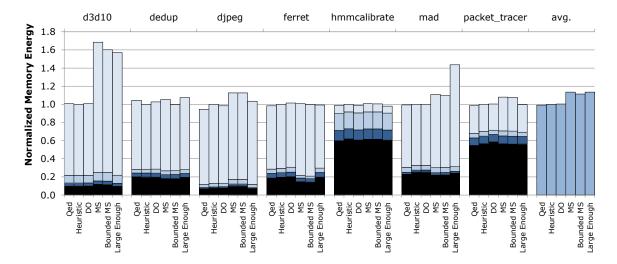

|                  |            | 5.5.2   | Energy Consumption                           | 134 |

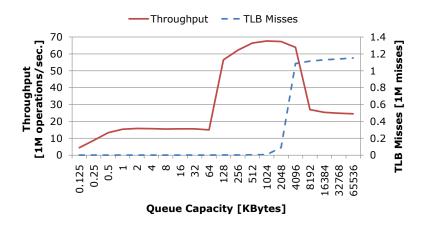

|                  |            | 5.5.3   | Discussion                                   | 135 |

|                  | 5.6        | Relate  | ed Work                                      | 141 |

|                  | 5.7        | Chapt   | ter Summary                                  | 143 |

| 6                | Conclusion |         |                                              | 144 |

|                  | 6.1        | Summ    | nary and Contributions                       | 144 |

|                  | 6.2        | Future  | e Directions                                 | 147 |

| Bibliography 151 |            |         |                                              |     |

# List of Tables

| 3.1 | Comparison of dynamic instruction placement algorithms | 37  |

|-----|--------------------------------------------------------|-----|

| 3.2 | Applications for SPM evaluation                        | 52  |

| 3.3 | SPM experimental setup                                 | 53  |

| 3.4 | Energy per SPM or FC operation                         | 54  |

| 4.1 | Applications for team scheduling evaluation            | 87  |

| 4.2 | Energy per operation for team scheduling evaluation    | 91  |

| 5.1 | Results of methods alternative to QED                  | 121 |

| 5.2 | Execution time results                                 | 133 |

| 5.3 | Energy per operation for QED evaluation                | 135 |

| 5.4 | A Guideline to select a queue design                   | 140 |

# List of Figures

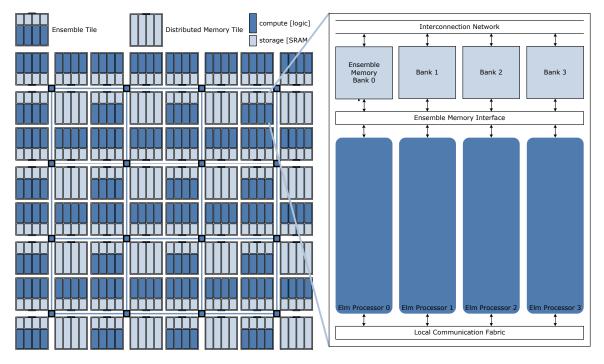

| 2.1  | The system-level Elm architecture                                                                                                    | 12 |

|------|--------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | The core-level Elm architecture $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                     | 14 |

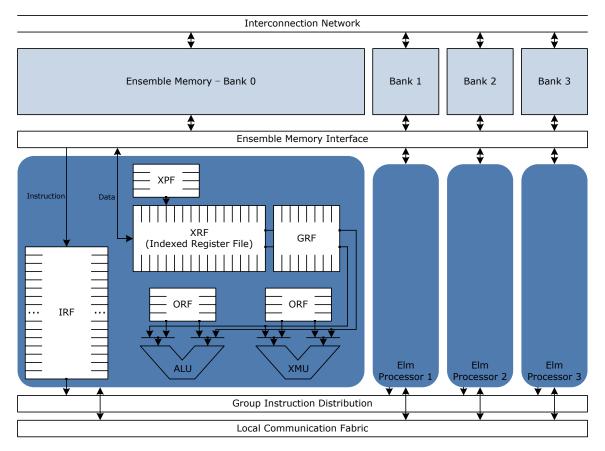

| 2.3  | The architecture of Elm programming system                                                                                           | 18 |

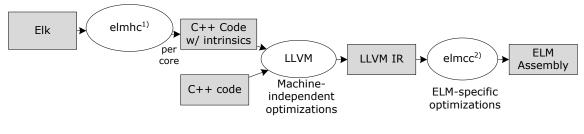

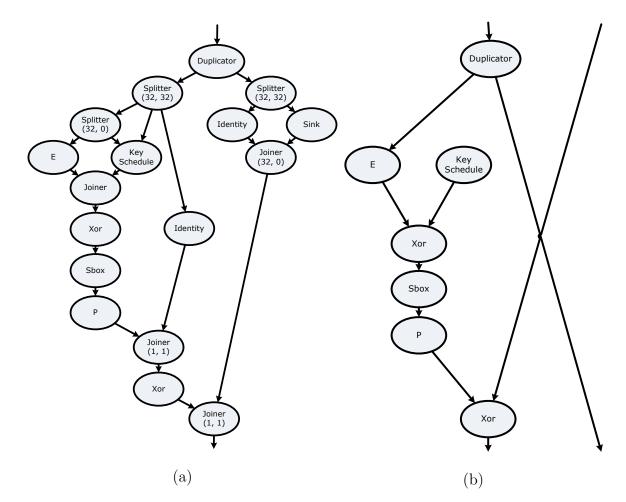

| 2.4  | DES with and without multiple input and output streams per actor $% \left( {{{\mathbf{T}}_{{\mathbf{T}}}}_{{\mathbf{T}}}} \right)$ . | 21 |

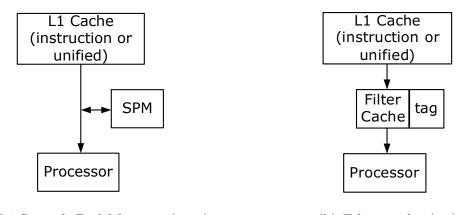

| 3.1  | L0 instruction stores                                                                                                                | 33 |

| 3.2  | An example fine-grain and coarse-grain instruction placement $\ldots$                                                                | 35 |

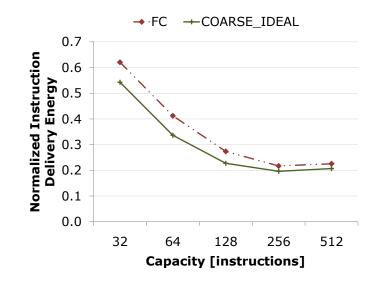

| 3.3  | Instruction delivery energy with an ideal coarse-grain placement $\ldots$                                                            | 36 |

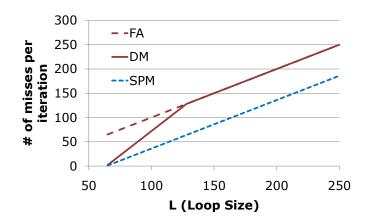

| 3.4  | Misses of SPMs and FCs for straight-line loops                                                                                       | 41 |

| 3.5  | Compiler's conservativeness with respect to SPM placement                                                                            | 42 |

| 3.6  | Pseudo code of our fine-grain instruction placement algorithm $\ldots$ .                                                             | 44 |

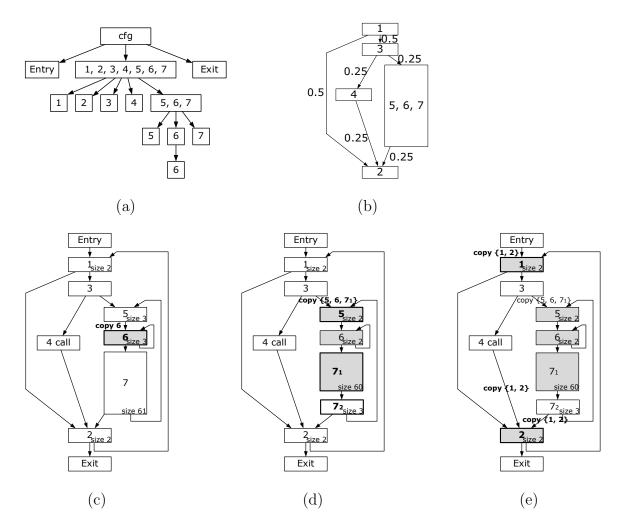

| 3.7  | An example of applying our fine-grain placement algorithm                                                                            | 46 |

| 3.8  | Adding launching-pads                                                                                                                | 49 |

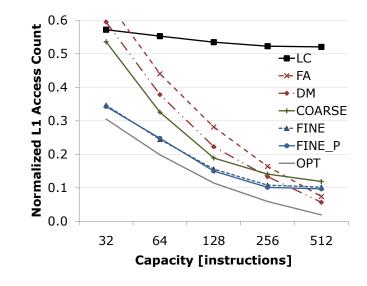

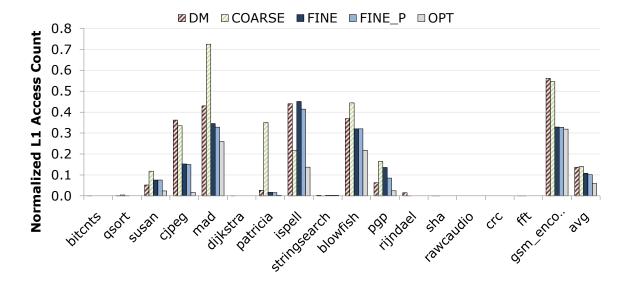

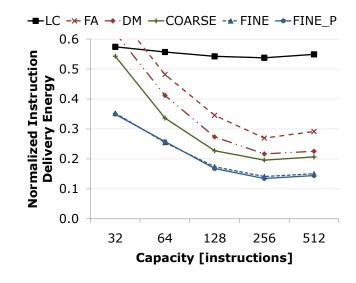

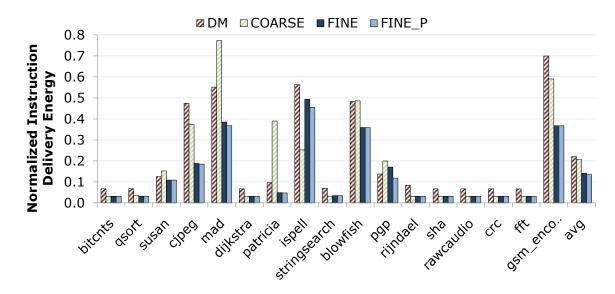

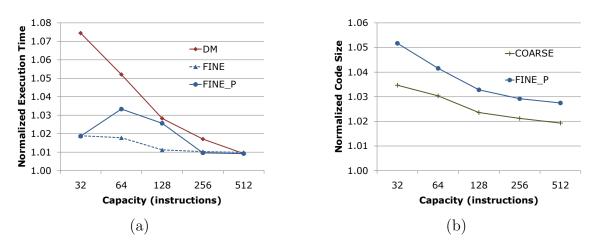

| 3.9  | L1 access and energy consumption results $\ldots \ldots \ldots \ldots \ldots \ldots$                                                 | 56 |

| 3.10 | Execution time and code size results                                                                                                 | 59 |

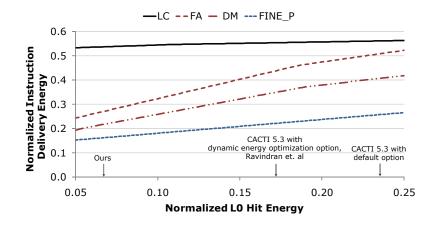

| 3.11 | Sensitivity of energy saving on the L0 to L1 access energy ratio $\ldots$                                                            | 60 |

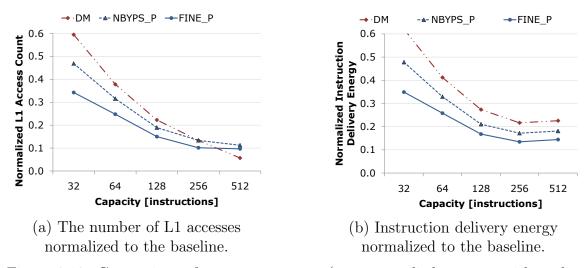

| 3.12 | Bypassing support results                                                                                                            | 61 |

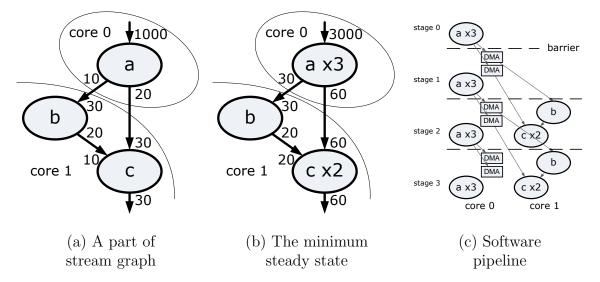

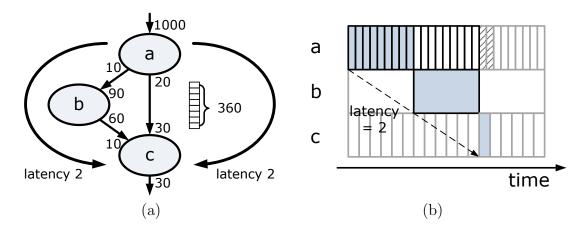

| 4.1  | An example of SGMS                                                                                                                   | 67 |

| 4.2  | An example of deadlock in a feedback path by SGMS                                                                                    | 69 |

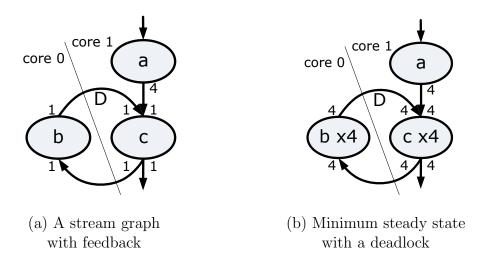

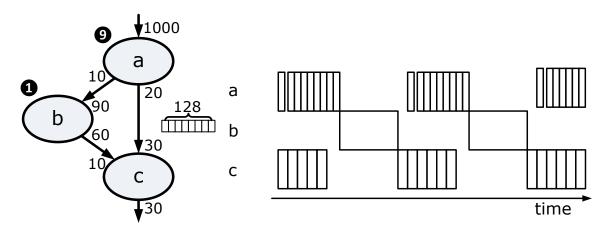

| 4.3  | An example team scheduling and its generated code                                                                                    | 71 |

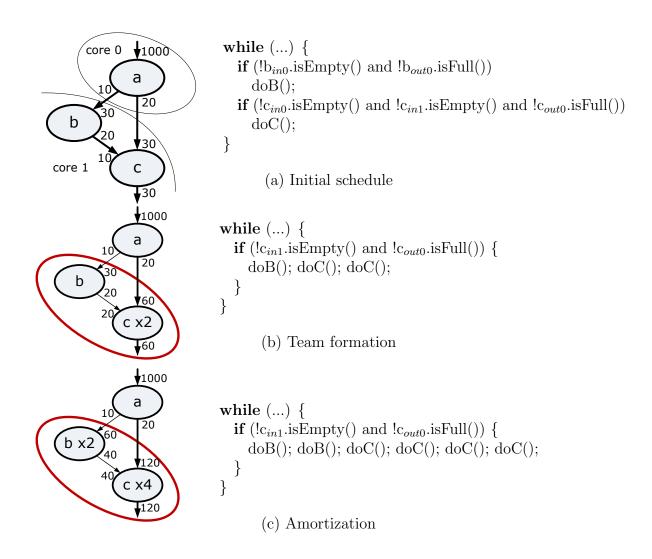

| 4.4  | Example deadlock and serialization from insufficient queue capacity .                                                                | 74 |

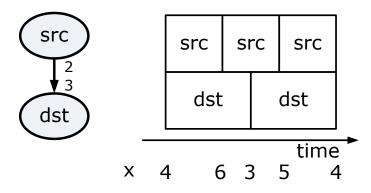

| 4.5  | A steady state of a producer-consumer pair                                                                                           | 75 |

| 4.6  | Illustration of queue capacity computation algorithm                                                                                 | 79 |

| 4.7  | Pseudo code of team scheduling $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 82  |

|------|--------------------------------------------------------------------------------------------------------|-----|

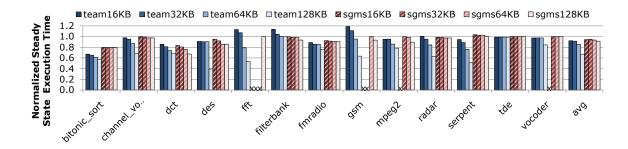

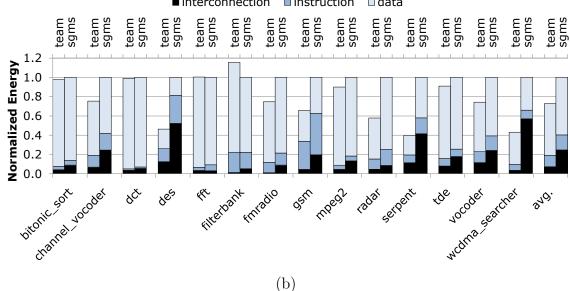

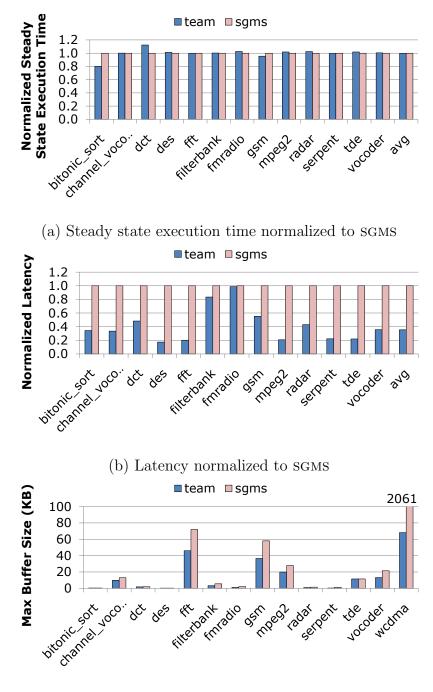

| 4.8  | Buffer space limited experiment results                                                                | 89  |

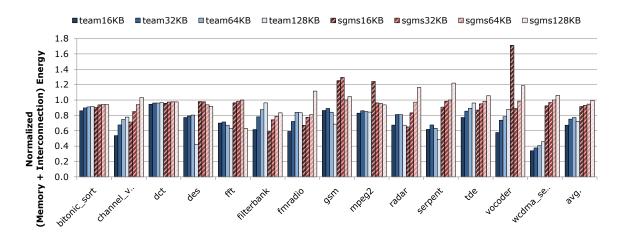

| 4.9  | Energy consumption results                                                                             | 90  |

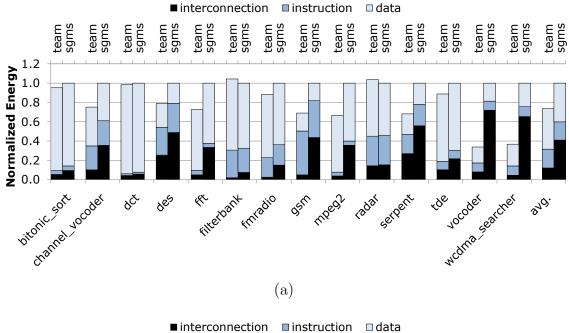

| 4.10 | Energy consumption breakdown                                                                           | 92  |

| 4.11 | Amortization factor limited experiment results                                                         | 95  |

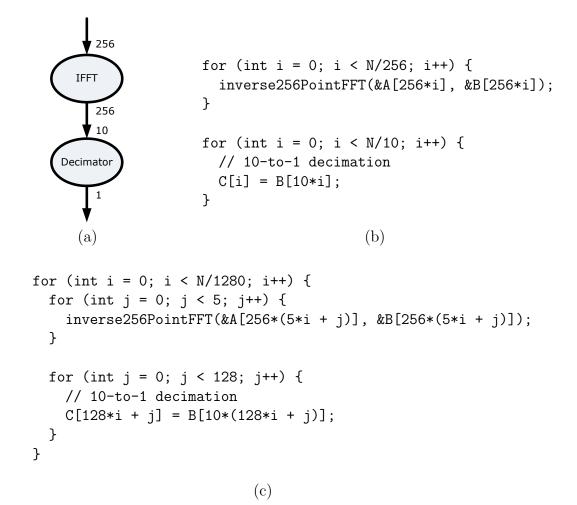

| 4.12 | A stream graph and its equivalent implementation in C $\ldots$ .                                       | 102 |

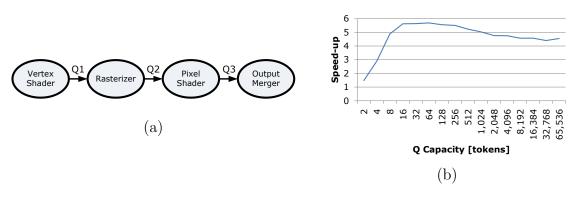

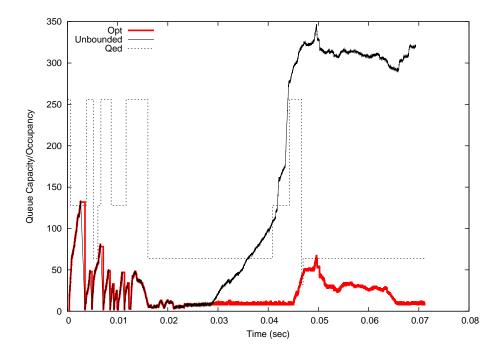

| 5.1  | Direct3D pipeline speed-up vs. queue capacities                                                        | 107 |

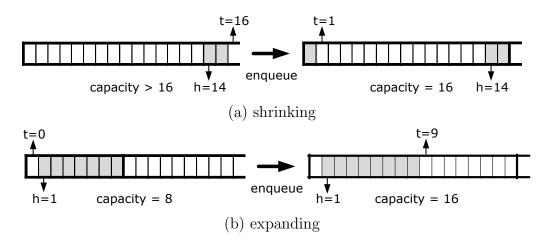

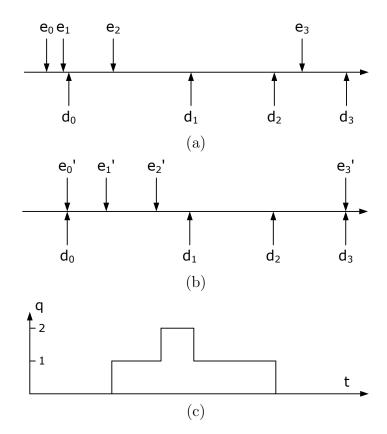

| 5.2  | Examples of capacity adjustment                                                                        | 110 |

| 5.3  | Capacity adjustment procedure                                                                          | 110 |

| 5.4  | Reserve-commit interface                                                                               | 111 |

| 5.4  | QED implementation                                                                                     | 115 |

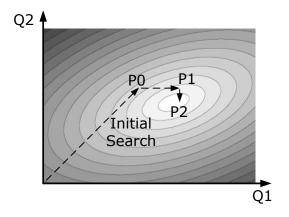

| 5.5  | Illustration of heuristic search procedure                                                             | 118 |

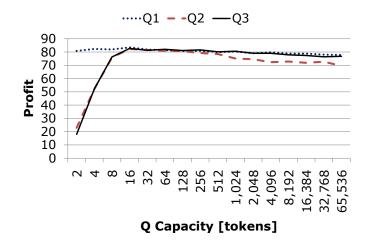

| 5.6  | The profit of d3d10 vs. queue capacities $\ldots \ldots \ldots \ldots \ldots \ldots$                   | 119 |

| 5.7  | Construction of dynamic optimal capacity adjustment                                                    | 123 |

| 5.8  | An example dynamic optimal capacity adjustment                                                         | 124 |

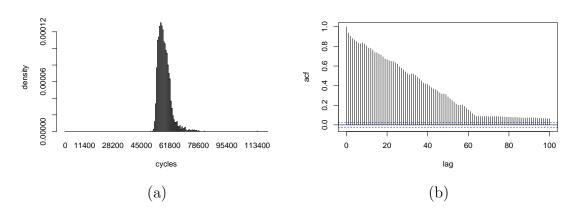

| 5.9  | Statistics of applications                                                                             | 127 |

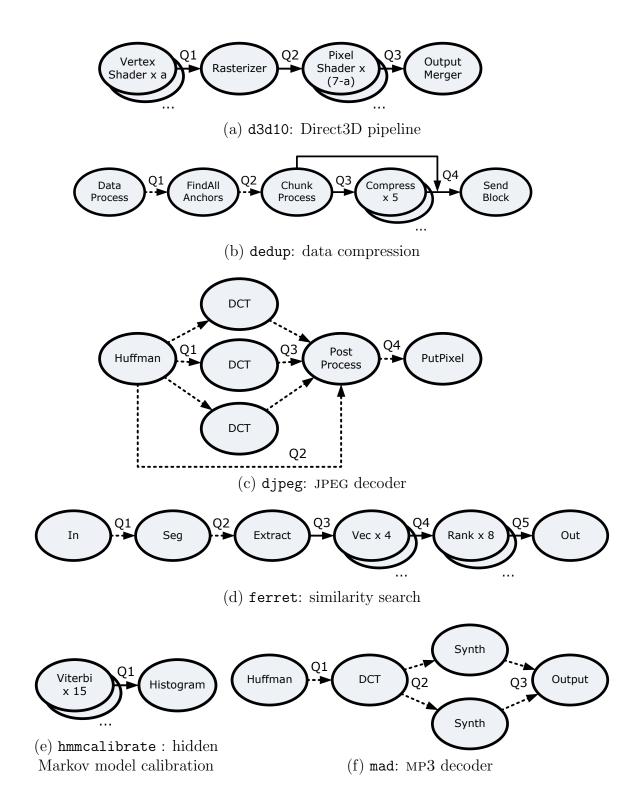

| 5.9  | Pipeline configuration of evaluated applications                                                       | 130 |

| 5.10 | Energy Consumption Results                                                                             | 136 |

| 5.11 | Capacity adjustment in dedup                                                                           | 137 |

| 5.12 | Throughput and TLB misses of a synthetic benchmark                                                     | 138 |

## Chapter 1

## Introduction

## 1.1 Motivation

#### Energy Efficiency Challenge in Embedded Computing

Improving energy efficiency is the one of the most critical challenges we face in contemporary computer architectures. In many domains, energy consumption is the primary constraint that prevents us from solving increasingly advanced problems that require ever higher computation power. The high performance computing community recognizes energy efficiency as the biggest challenge to achieve exa-scale computing that facilitates important scientific understandings such as global climate change, safe nuclear reactor design, and drug discovery [89]. Data centers consumed 1.5% of the total US energy use in 2006 [150]. Their electric bills for three years are comparable to hardware costs [106], and the proportion of electric bills in the total cost of ownership is expected to grow [17].

Energy efficiency plays a similarly, if not more, crucial role in embedded computing [34]. The energy efficiency of embedded devices directly affects their usability since many of them are operated by batteries. The capacity of batteries is not significantly improving [11], and they are limited by embedded devices' tight constraints with respect to form factor and manufacturing cost. This energy constraint conflicts with increasing computation demands of embedded devices as they adopt more sophisticated algorithms [137,152] and target wider application areas, sometimes substituting for personal computers.

In order to satisfy the demanding computation requirement within acceptable energy efficiency, application-specific integrated circuits (ASICs) are often required [59, 73]. Unfortunately, as semiconductor processes advance, non-recurring engineering costs of designing, implementing, and testing a new ASIC become extremely high [109]. This is particularly problematic in domains such as medical equipment, which cannot afford the excessive cost of ASIC due to their limited market size [12].

The Elm project, in which the work described in this dissertation was conducted, aims to design a programmable system that avoids excessive non-recurring engineering cost while achieving energy efficiency comparable to that of ASICs. Although this is an ambitious goal which has yet to be met, this dissertation presents a few important steps toward the goal with respect to software mechanisms that efficiently manage the memory subsystem.

### The Role of Software in Improving Energy Efficiency of Instruction and Data Delivery

In order to close the efficiency gap between ASICs and programmable processors, the inefficiencies in conventional programmable processors should be identified first. Balfour et al. [13] show that 42% and 28% of the energy is consumed for instruction and data delivery, respectively, in an embedded processor based on 32-bit SPARC architecture [58]. Balfour's thesis [12] also shows that the energy consumed for executing an **add** instruction is at least  $10.2 \times$  the energy expended in a 32-bit adder. In other words, it is instruction and data delivery, not computation, that contributes to most of the energy consumption in embedded processors. Consequently, the energy efficiency of the memory subsystem through which instructions and data are delivered must be improved to close the efficiency gap.

A central theme of this dissertation is that the compiler and run-time system can significantly improve the energy efficiency of delivering instructions and data by efficiently managing resources whose controls are deliberately exposed to software. This energy efficiency improvement relies on the compiler or run-time system's ability to reason about the locality of instruction and data access, which allows optimizations that save energy. Examples include avoiding tag checks by proving that the target instruction is already cached and using statically-allocated arrays by proving a tight bound on buffer capacities to avoid dynamic allocations. Of course, this software-based approach is not a silver bullet and should be complemented by other mechanisms such as dynamic voltage scaling [162], gating [129, 143], and hardware customization [48, 59]. It is also important to know what kind of facts the compiler and run-time system can prove for energy efficiency and which of them yields the largest gain. This dissertation focuses on two optimization opportunities found in the Elm project that lead to large energy savings, are not satisfactorily handled by existing approaches, and are algorithmically interesting. Brief descriptions on other optimizations investigated in the Elm project are provided in Section 2.1.

### Improving Energy-efficiency of Instruction Delivery by Compiler-managed Instruction Scratch-pad Memory

Instruction delivery accounts for the largest fraction of the energy consumed by embedded processors according to Balfour et al. [12,13]. Similarly, the instruction cache contributes to 27% and 29% of the total energy consumed in StrongARM [115] and TM3270 TriMedia VLIW processors [151], respectively. A typical instruction cache has high energy consumption because it occupies a significant fraction of the processor die area and is accessed every cycle.

Researchers have observed that the current cache hierarchy is primarily optimized for performance, and that extending the hierarchy by adding small caches (typically 1KB or smaller) between the L1 instruction cache and the processor saves energy [84]. Energy efficiency can be further improved by replacing the small caches with scratchpad memories (SPMs), which we call L0 instruction SPMs. SPMs are compiler-managed stores in which no tags are used to associate locations in SPMs and therefore consume less energy per access than caches with the same capacity. Small caches between the L1 instruction cache and the processor are natural targets to be replaced with SPMs since the typical locality captured by such small stores comes from loops, which are analyzable by the compiler. Chapter 3 describes a compiler algorithm that manages L0 instruction SPMs and evaluates their energy savings compared to cache-based designs and previous SPM management algorithms.

#### Improving Energy-efficiency of Data Delivery in Stream Applications

Data delivery energy accounts for the second largest fraction of the energy consumed by embedded processors [12, 13]. Since data accesses typically have higher miss rates than instructions, data locality optimizations have a larger impact on the performance. In addition, data locality optimizations have intimate relation to efficient parallelization. Therefore, data locality optimizations have been extensively studied [44, 45, 94, 104, 105, 135, 164], even though they pose challenges not found in analyzing locality of instructions: in contrast to instructions of a read-only nature, dependencies must be preserved with respect to data writes, which often involves inter-procedural pointer aliasing analyses. This dissertation focuses on a relatively understudied yet an important data locality optimization problem in the embedded domain — minimizing buffer space while sustaining the throughput of parallelized stream applications. Stream applications are commonly found in the embedded domain, whose typical examples are digital signal processing algorithms.

In embedded stream applications, pipeline parallelism plays a critical role in achieving satisfactory parallelization speed-ups. Embedded applications tend to process data sets smaller than those processed by high-performance computing counterparts. Consequently, solely exploiting data-level parallelism is not enough to fill increasing number of cores [51]. In addition, components such as the arithmetic encoder in H.264 or the Huffman encoder in JPEG or MP3 are not data parallel, and pipelining is typically the only type of parallelism that can be exploited. Even a small number of non data-parallel components can significantly limit the scalability of approaches that solely exploit data-level parallelism [51]. When pipeline stages contain large local states (e.g., texture data of pixel shaders in graphics pipelines), accessing the states from a few dedicated cores using pipeline parallelism can yield better locality than swapping in and out the states using only data-level parallelism [90]. Moreover, pipelining is also an effective form of parallelization for heterogeneous architectures. We can map a stage to the component where it can be efficiently executed. When there is a pipeline stage that is a prominent bottleneck, hardware that is highly optimized for that particular stage can be incorporated (e.g., a rasterizer in a graphics pipeline).

Efficient pipeline parallelization however poses several challenges. Whereas challenges such as load imbalance can be resolved by existing load balancing scheduling algorithms such as work stealing [29], appropriately sizing queues between stages has been relatively understudied. Arbitrary "large enough" numbers are often chosen for inter-stage queue capacities. The queue capacity computation has particularly important consequence on energy efficiency, since queues too large will incur considerable amount of costly accesses to remote or off-chip memories. On the other hand, queues should have large enough capacities (e.g., double buffering) so that producers and consummers can work in parallel or the run-time variation of pipeline stages can be hidden. This is an example of traditional trade-off between storage and parallelism [8]: just as using more registers allows for more instruction-level parallelism, using more memory in inter-stage queues allows for more pipeline parallelism. Chapter 4 describes a compiler analysis that computes the minimum queue capacity that maximizes the throughput of static stream applications, applications in which production and consumption rates of stages are close to compile-time constants. Chapter 5 describes a dynamically-sized array-based concurrent queue design for dynamic stream applications.

## **1.2** Contributions

This dissertation makes six contributions: The first is a mechanism to reduce instruction delivery energy; the subsequent three are mechanisms to reduce data delivery energy in stream applications. The last two are with respect to infrastructure built for the Elm project.

#### Instruction Scratch-pad Memory Management (Chapter 3)

This dissertation presents a compiler algorithm that manages instruction scratch-pad memories (SPMs), whose instruction delivery energy saving is estimated to be 87%. In contrast to the previous SPM management algorithms, instruction SPMs with our algorithm achieve not only a lower access energy but also lower miss rates compared to caches with the same capacity. This ensures consistently higher energy efficiency than a competing design called filter caches over diverse memory hierarchy configurations found in embedded processors. In addition, I discuss reasons for the failure of previous algorithms to consistently achieve energy savings over filter caches, namely, because they neglect the conservative nature of compilers, unjustifiably rely on integer linear programming formulations, or do not take rigorous care in evaluation designs.

#### Queue Capacity Computation for Static Stream Applications (Chapter 4)

This dissertation presents a static analysis that computes minimum inter-actor queue capacities that sustain the maximum throughput of static stream applications. This analysis allows to reduce data delivery energy by minimizing costly remote or off-chip memory accesses while avoiding throughput degradation and deadlocks.

#### Buffer-space Efficient Static Stream Scheduling (Chapter 4)

This dissertation presents a static stream-scheduling algorithm called *team scheduling* that minimizes communication and synchronization overhead while avoiding costly remote or off-chip memory accesses, which in turn saves considerable data delivery energy in static stream applications. It is estimated that the team scheduling can achieve 27% higher throughput while requiring 33% less energy for data delivery than a previous stream-scheduling algorithm called SGMS [90] in a 16-core Elm processor. The team scheduling is based on the queue capacity computation analysis mentioned above, which allows to flexibly apply transformations that minimize communication and synchronization without incurring too large queues, throughput degradation, or deadlocks.

#### Dynamically-sized Queues with Minimal Memory Footprint (Chapter 5)

This dissertation presents a concurrent queue data structure called QED (Queue Enhanced with Dynamic sizing) that adjusts its capacity at run-time to maximize the throughput while minimizing the memory footprint of inter-actor queues, which in turn reduces the data delivery energy in dynamic stream applications. Whereas the queue capacity computation analysis mentioned above minimizes the memory footprint in parallel execution of static stream applications, QED does the same for dynamic stream applications. It is estimated that QED can achieve an average of 18% speed-ups and 15% savings in data delivery energy compared to a linked-list based queue design.

#### The Elk Stream Programming Language (Chapter 2)

This dissertation presents a stream programming language called Elk that is extended from StreamIt [145]. Compared to StreamIt, Elk supports multiple input and output streams per actor, which allows representations with less clutter in applications such as Data Encryption Standard. In addition, Elk uses array notations to access input and output stream tokens instead of **push**, **pop**, and **peek** primitives in StreamIt. Our experience tells us that the array notation leads to more concise programs and easier compiler implementation.

#### Programming System for the Elm Architecture (Chapter 2)

This dissertation presents a programming system infrastructure for the Elm architecture. The programming systems facilitates architecture evaluations [12] and demonstrates that a primary goal of the Elk project — efficient but *programmable* architecture — can be met with reasonable effort (i.e., primarily one Ph.D. student plus one to two M.S. students).

## 1.3 Collaboration

This dissertation describes work that was performed as part of the Elm project. James Balfour was the main architect of the Elm architecture, and I collaborated with him on the Elm cycle-accurate simulator that he designed. The Elk stream language is based on the initial design by him, whose features include array notations for accessing input/output streams.

David Black-Schaffer proposed a stream programming model called "Block Parallel Programming" [26, 28] that is an alternative to existing stream programming models such as StreamIt [145] and StreamC/KernelC [110]. His work inspired parts of the Elk programming system, such as supports for multiple input/output streams per actor, real-time constraints propagation, and physical core mappings with simulated annealing.

James Balfour, Curt Harting, and James Chen provided the numbers for the energy expended in circuit components, on which most of the estimated energy consumption presented in this dissertation is based. David Black-Schaffer did an initial investigation on instruction SPMs [27], and Clinton Buie participated in initial discussions on our instruction SPM algorithm. Youngsik Kim helped build a converter from LLVM [95] intermediate representation to our intermediate representation. Jooseong Kim implemented the front-end of the Elk compiler and helped on debugging our Elm C++ compiler back-end. Keiji Matsumoto, a visitor from Renesas Technology, examined the partitioning step of SGMS [90] that is formulated as integer linear programming. The QED presented in Chapter 5 was discussed with Jiwon Seo.

## 1.4 Organization

The remainder of this dissertation is organized as follows:

Chapter 2 describes the Elm project, in which the work presented in this dissertation was performed. The programming system for the Elm architecture consists of two layers. The lower layer is a C++ compiler that effectively targets the microarchitectural features of Elm. The upper layer is a stream programming system that efficiently utilizes system-level features of Elm such as software-managed memories with DMA operations. The upper layer compiles a language called Elk that extends StreamIt [145]. Although the algorithms presented in the subsequent chapters are not Elm-specific, this chapter provides useful context to facilitate understanding them.

Chapter 3 presents a compiler algorithm that manages instruction scratch-pad memories (SPMs). Energy efficiency, miss-rates, execution times, and code size are compared with SPMs managed by previous algorithms, filter caches, and loop caches. We use MiBench [55] applications and the Elm cycle-accurate simulator for the comparison.

Chapter 4 presents a compiler analysis that computes the minimum inter-actor queue capacities that sustain the maximum throughput of static stream applications. Chapter 4 also presents a static stream-scheduling algorithm, called team scheduling, based on the analysis. Energy efficiency and execution times are compared with those of a previous scheduling algorithm called SGMS. We use StreamIt [145] benchmark applications and a simulated 16-core Elm processor for the comparison.

Chapter 5 presents a dynamically-sized array-based concurrent queue design called QED (Queue Enhanced with Dynamic sizing) that minimizes the memory footprint of inter-actor queues in dynamic stream applications, which is complementary to the mechanism described in Chapter 4. Energy efficiency and execution times are compared with those of a popular linked-list based design called Michael and Scott's queue [112] and array-based statically-sized queues with "arbitrary large" capacities. We use applications selected from GRAMPS [141], MiBench [55], and SPEC benchmarks for the comparison.

Chapter 6 summarizes the dissertation, focusing on insights obtained with respect to software and hardware coordination for energy efficiency. This dissertation concludes with discussion on future directions that can improve the work presented.

## Chapter 2

# The Elm Project and Its Programming System

The work described in this dissertation has been done in the context of the Elm (Embedded Low-power Microprocessor) project, whose main goal is closing the energyefficiency gap between programmable embedded processors and application-specific integrated circuits (ASICs). As presented in the previous chapter, the Elm project identified the main energy consumption source to be instruction and data delivery, not computation itself. This motivates using the memory subsystem in a more energy efficient manner by software, which is the main objective of this dissertation. However, software-only approaches are often insufficient to target the energy efficiency of ASICs, and synergistic efforts between hardware software are often desired. For example, the energy reduction that is achieved by the instruction scratch-pad memory management algorithm presented in Chapter 3 partially stems from features provided by instruction scratch-pad memories in the Elm architecture. Similarly, the static scheduling algorithm that minimizes buffer space overhead presented in Chapter 4 relies on efficient direct memory access (DMA) operations provided by the Elm architecture.

This chapter first briefly overviews the Elm architecture (Section 2.1), focusing on its impact on, and interaction with, the programming system. For comprehensive introduction to the Elm architecture, the readers are referred to Balfour's thesis [12]. Section 2.2 describes the programming system for the Elm architecture, which consists of two layers. The lower layer is a C++ compiler called elmcc, which leverages the LLVM compiler infrastructure [95]. The instruction scratch-pad memory management algorithm presented in Chapter 3 is implemented as a part of elmcc. The upper layer is a stream programming system called Elk that is extended from StreamIt [145]. The static stream-scheduling algorithm presented in Chapter 4 is implemented in the Elk compiler.

## 2.1 Elm Architecture Overview

The Elm architecture is designed for exploiting parallelism and locality abundant in embedded applications to achieve high energy efficiency. The fine-grain control of architectural resources is exposed to software so that the complexity of embedded systems design can be amortized in the compilers and programming tools, avoiding the design and verification cost of special-purpose hardware incurred for each new system. It was estimated that an Elm system implemented in a 45nm CMOS processor would deliver 500 GOPS at less than 5W in about 10mm  $\times$  10mm of die area (this estimation is based on the register-transfer level (RTL) model presented in Appendix A.2 of Balfour's thesis [12]). In comparison, it was estimated that an embedded processor based on 32-bit SPARC architecture [58] delivers about 380 MOPS at 36mW in 0.5mm  $\times$  0.3mm of die area, which means that an Elm processor achieves about 7 $\times$ the energy efficiency per performance and 2 $\times$  the area efficiency per performance [12] compared to the SPARC-based embedded processor.

### 2.1.1 System-level Architecture

Figure 2.1 illustrates the system level architecture of Elm. An Elm system consists of tiled cores (i.e., processors) that are grouped into ensembles and connected with a mesh on-chip interconnection network. In addition to core tiles, an Elm system also has distributed memory tiles.

Figure 2.1: The system-level Elm architecture [12].

#### Distributed Software-managed Memory and Cache Memory

The processors communicate over an on-chip interconnection network with a mesh topology. Elm allows software to control the placement and transfer data directly (i.e., via DMA) between ensemble memories. Multiple outstanding DMA transfers can be issued so that a sufficient amount of communication time can be overlapped with computation. Scatter-gather DMA transfers are also provided to minimize the overhead of communication. Software-managed placement and non-blocking scatter-gather DMAs are particularly useful for stream applications whose communication patterns are analyzable by the compiler. These features are exploited by several stages of the Elk stream compiler, including the team scheduling phase presented in Chapter 4.

These software-managed ensemble memories are backed by a collection of distributed memory tiles, which can be configured as caches. These cache memories are useful for capturing the type of locality that is not easily statically analyzable.

#### **Ensemble Structure**

As illustrated in Figure 2.1, four processors are grouped into *ensembles*, the primary building block of the Elm architecture. The motivation behind this grouping is to share expensive resources such as a local memory and an interface to the interconnection network. In addition, low-overhead communication and synchronization mechanisms are provided between the processors within an ensemble so that the compiler or the run-time system can exploit the locality between tightly coupled tasks mapped to the same ensemble.

Processors in the same ensemble share an ensemble memory, which corresponds to the L1 cache in conventional embedded processors. The ensemble memory provides a low latency access due to its proximity, while allowing concurrent access to the local processors and the network interface by through its bank structure. Processors within an ensemble are also connected through a local communication fabric with high-bandwidth point-to-point links, which can be used to capture predictable communications which demand low latency and high bandwidth.

These low-overhead communication mechanisms allow the programming system to exploit the parallelism of tightly coupled tasks even if their communication-tocomputation ratio is so high that the benefits of parallelization are typically more than offset by the overhead of conventional cache coherent memories. For example, pipeline stages that communicate a considerable amount of data (e.g., back-end pipeline stages of the graphics rendering pipeline) can be mapped to the same ensemble so that the low-overhead local communication fabric can be used. When a task has enough instruction-level parallelism (ILP), four processors in an ensemble can be used as an ILP core with four coupled instruction streams, as the RAW processors are used as ILP machines [101]. An ensemble can also be used as a SIMD processor using the concept of *processor corps*. Processors operating as a processor corps execute the same instruction, amortizing the cost of instruction fetch.

Unfortunately, the ensemble structure is not fully exploited by the current Elm programming system, and, therefore, we used hand-optimized code to evaluate features associated with the ensemble structure. This is mostly because of limited time

Figure 2.2: The core-level Elm architecture [12].

and resources, which we decided to use for targeting architectural features that result in a higher impact. Although ensemble level optimizations can result in a large energy-efficiency gain, their scalability is limited to four processors, and most of the optimizations are only a matter of implementing existing algorithms: e.g., we can use an ensemble as an ILP core using the algorithm described by Lee et al. [101], and the SIMD mode can be used by employing affine partitioning algorithms for data-parallel loops as described by Feautrier, Lim, and Lam [44, 45, 105]. Instead, we focus on architectural features that are not satisfactorily handled by existing algorithms (as in Chapter 3) or that support scalable parallelism (as in Chapter 4).

#### 2.1.2 Micro-architecture

Figure 2.2 illustrates the core-level architecture of an Elm system. The Elm cores are statically scheduled dual-issue 32-bit processors. Each of them has two functional units, ALU and XMU. While the ALU executes generic computation instructions, the XMU is specialized for memory, control, communication, synchronization, and a few simple arithmetic (e.g., add and sub) instructions.

#### Efficient Instruction Delivery: Instruction Scratch-pad Memory

One of the most distinguished feature of the Elm processor is that instructions are issued from compiler-managed scratch-pad memories (SPMs). In Elm, we call the scratch-pad memories *instruction register files* (IRFs) to emphasize their specialization for instruction fetches and small capacity (typically 64-256 instructions). The compiler is responsible for making sure that instructions are transferred to the instruction scratch-pad memory before they need to be issued, thereby eliminating the need for tags. Eliminating tag checks significantly reduces the energy per access, particularly for small caches where long tags are needed. For example, Section 3.5.1 shows that eliminating tag checks of a 256-instruction direct-mapped cache saves 53% of the read access energy.

Instructions are transferred from the ensemble memory in blocks whose length, source location, and target location are specified by the compiler. The processor continues to execute during instruction transfers, decoupling issuing and transferring instructions. This allows the compiler to pre-transfer instructions to hide the latency of instruction transfers. Instruction scratch-pad memories filter out a significant fraction of instruction fetches, enabling a single read and write port design of the ensemble memory, which is another major energy efficiency improvement.

Chapter 3 presents a compiler algorithm that places instructions at appropriate SPM locations to minimize conflict misses and inserts instructions that dynamically transfer instructions from backing memories (the ensemble memory in Elm) to SPMs. Even though there have been numerous compiler algorithms for managing instruction SPMs, Chapter 3 shows that SPMs managed by these previous algorithms cannot achieve clearly higher energy efficiency than caches with the same capacity. Chapter 3 elaborates on the reasons behind the unsatisfactory results of previous SPM placement algorithms and shows how our algorithm realizes noticeable energy savings compared to caches.

Instruction SPMs in Elm provide useful features that further improve the effectiveness of the SPM placement algorithm presented in Chapter 3. As mentioned above, decoupling issuing and transferring instructions allows the algorithm to hide the latency of instruction transfers, thereby improving the execution time. In addition, the instruction SPMs in Elm provide wrap-around access: when the target SPM location plus the transfer block length exceeds the capacity of the SPM, the target location wraps around to the beginning of the SPM. This considerably reduces the fragmentation of instruction placement in SPMs.

On the other hand, we find that not all features provided by the instruction SPMs in Elm are clearly beneficial with respect to energy efficiency. The instruction SPMs in Elm do not allow bypassing. In other words, all instructions must be issued from the SPMs, and there is no bypass that can be used for issuing instructions directly from the backing memory. In Section 3.6, we show that adding bypass support reduces the number of accesses to the backing memory by 40%, and the energy consumed for accessing the SPM and the backing memory cells by 31%. It is true that removing bypass support has several advantages such as simpler connectivity and a shorter program counter. However, it is unclear that these advantages will more than offset the aforementioned 31% energy saving of bypass.

#### Efficient Data Delivery

**Operand Register File** As shown in Figure 2.2, Elm processors have distributed and hierarchical register organization. Each function unit has a small local register file called an *operand register file* (ORF), which is backed by the *general-purpose register file* (GRF). ORFs capture short-term data locality so that a considerable number of operand accesses can be provided by inexpensive registers that are small and close to the functional units. ORFs also filter out a significant fraction of bandwidth demand for larger and more expensive GRFs. This allows to keep the number of read and write ports of the GRF small (note that this is similar to the idea behind reducing the number of read and write ports of the ensemble memory by filtering out instruction accesses by the instruction SPMs). The ORF concept is extended to explicitly forward temporary values through result registers to avoid writing dead values back to ORFs or GRFs.

We allocate registers and schedule instructions using conventional algorithms. We first schedule instructions assuming an infinite number of registers using the list scheduling algorithm. The purpose of this initial schedule is to balance the load of two functional units and to estimate the pressure of ORFs. Then, we allocate registers using the conventional graph coloring register allocation algorithm [33] for each register file, starting from smaller ones. The initial schedule imposes constraints on register allocation with respect to limited connectivity between register files and functional units. For example, the XMU cannot read the ALU'S ORF, and, therefore, variables that are read by instructions that execute on different functional units must be assigned to the GRF or duplicated to multiple ORFs. To effectively utilize the ORFs, we use the spill cost function that prefers variables with a high access frequency and short life time. Since register allocation and instruction scheduling for distributed and hierarchical register organization in Elm is a straightforward combination of existing approaches, this dissertation does not go into the further details. Those who are interested in the details are referred to Balfour et al. [12, 14].

In our initial design of the Elm architecture presented in Balfour et al. [13] and Dally et al. [38], we took a radical approach to the distributed and hierarchical register organization, where the connectivity is more limited. For example, functional units are not allowed to directly access the GRF and every operand must go through ORFs. This limited connectivity combined with explicit pipelining of instructions [13, 38] makes the instruction scheduling and register allocation considerably more tightly coupled than conventional architectures. In order to avoid a severe phase ordering problem between register allocation and instruction scheduling, a unified allocation and scheduling approach was desired. Therefore, we developed *path finding scheduling* (an algorithm presented in a separate technical report [125]), which simultaneously solves the allocation and scheduling problem by finding paths through a graph

elmhc: elm high-level compiler

elmcc: elm low-level compiler that accepts C++ code

Figure 2.3: The architecture of Elm programming system.

that describes the connectivity of resources. However, in the aim to avoid potential scheduling deadlocks resulting from simultaneous allocation and scheduling, the algorithm was made to be too complicated and slow (even through it is a polynomial-time algorithm). This motivated the current simpler distributed and hierarchical register organization in Elm.

Indexed Register File In additional to its distributed and hierarchical nature, register organization in Elm provides indirect access [14, 126]. The *indexed register file* (XRF) is indirectly accessed through the *index pointer registers* (XPs). The XRF allows to block data into registers, as we block data into caches [94]. Although it is possible to block data into registers without indirect access support, doing so involves loop unrolling, which degrades the instruction locality. The XRF also supports bulk transfers to/from the ensemble memory, which can be viewed as DMAs between the ensemble memory and the XRF.

## 2.2 Elm Programming System

Figure 2.3 illustrates the architecture of Elm's programming system. There are primarily two ways of using the programming system. When the target application follows the stream programming model, one can use a stream programming language called Elk. The high-level Elk compiler called elmhc compiles Elk code and generates C++ code per core. Architecture-dependent features such as DMA operations are exposed as intrinsic function calls, which are generated by elmhc during its code generation phase. When direct control of the architecture-dependent features is desired, or when the target application does not follow the stream programming model, the programmer can write C++ code per core. In this case, the programmer must manually use intrinsic functions to access architecture-dependent features.

Section 2.2.1 describes the low-level C++ compiler called elmcc, and Section 2.2.2 describes the high-level Elk compiler called elmhc.

#### 2.2.1 Low-level Compiler Back-end

The Elm C++ compiler (elmcc) is implemented as a back-end of the LLVM compiler framework [95]. The LLVM compiler parses C++ code, applies machine-independent optimizations, and emits optimized LLVM intermediate representation (IR). Several Elm-specific optimizations are implemented in elmcc, and its total line count is about 110K. Elm-specific optimizations include XRF bulk transfer generation, allocation of distributed and hierarchical register files, explicit forwarding generation, and instruction scratch-pad memory management. Chapter 3 describes the instruction scratchpad memory management in detail; other Elm-specific optimizations are described briefly in Section 2.1.2. The quality of code generated by elmcc is high enough that the efficiency of Elm architecture is mostly evaluated using compiled code in Balfour's thesis [12]. MiBench [55] and StreamIt [145] benchmarks whose line counts are up to tens of thousands are successfully compiled to produce correct results.

#### 2.2.2 High-level Parallelizing Stream Programming System

#### Elk Stream Programming Language

Among different kinds of parallelism that can be exploited by stream programming, a class of stream programming languages focus on data-level parallelism, which can be found from computations whose successive iterations are independent of each other. In domains where data-parallel computations are common and the data set is large enough, solely exploiting data-level parallelism often results in a near perfect utilization of all cores. Scientific computation is an example of such a domain and Sequoia [43] is an example of a stream programming language that focuses on datalevel parallelism.

Each computation chunk of common embedded applications operates on data sets that are smaller than those of scientific applications, and, therefore, data-level parallelism is sometimes not enough to achieve a degree of parallelism required to fully utilize the computing power of emerging multi-core processors. In addition to data-level parallelism, task-level and pipeline parallelism also should be exploited [51]. To the best of our knowledge, StreamIt [145] is the current state-of-the-art language that exposes data-level, task-level, and pipeline parallelism of streaming applications together to the compiler.

**Comparison with StreamIt** The Elk stream programming language extends StreamIt to address the issues discussed below. For the further details on constructs of StreamIt, refer to Thies et al. [145]. Black-Schaffer's thesis [26] provides an excellent literature review on stream programming systems other than StreamIt.

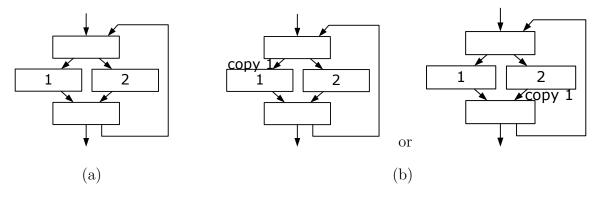

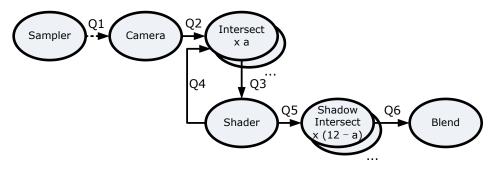

Single Input and Output Stream per Actor: StreamIt allows at most one input and output stream per actor. This constraint introduces unnecessary clutter in many applications. For example, Figure 2.4(a) shows a stage of DES (Data Encryption Standard) implemented in StreamIt, which includes several splitters, joiners, and identity actors that would have been unnecessary if actors with multiple input and output streams were supported as shown in Figure 2.4(b). Note that, in Figure 2.4(a), a spurious splitter (the producer of KeySchedule) is used to work around the lack of no-input-stream actors. Also, note that joiners are used before Xor actors to interleave two streams. While implemented the Xor actor, the programmer must keep in mind that even input tokens are from the first input stream to the joiner and odd input tokens are from the second one.

The rationale for restricting the number of stream inputs and outputs per actor in StreamIt was to restrict the methods of actor composition to pipeline, splitjoin, and feedback. In Thies et al. [145], the authors make an analogy to structured programs (i.e., programs without gotos), and argue that the restricted composition

Figure 2.4: A DES stage with (a) single input and output actors as in StreamIt and (b) multiple input and output actors as in Elk.

methods facilitate well-structured programs and simplify compiler analyses. However, experience from programming more than 20 representative applications has shown me that allowing arbitrary actor connections does not lead to undisciplined structuring of stream programs and that the limited expressiveness of StreamIt on actor connectivity does more harm than good. A single generic composition construct, such as **bundle** in Elk, which will be described shortly, is enough for writing well-structured stream programs. My experience from the Elk compiler implementation has also shown me that the restricted compositions do not necessarily simplify compilation. For most compiler analyses and transformations, the composition hierarchy should be flattened anyway to data structures such as *stream graphs* [90] that represent the connectivity of actors in the entire application. Compiler analyses occasionally need to find topological structures such as **splitjoins** or **feedbacks**, but such structures can be easily identified from flattened graphs by simple graph algorithms that have been commonly used by traditional compiler analyses without relying on explicit specification in source code.

**Push, Pop, and Peek Primitives:** In StreamIt, an actor produces and consumes stream tokens through **push** and **pop** primitives. StreamIt also provides a **peek** operation that allows an actor to read more input tokens than it consumes, which implies buffering on input stream tokens. For example, the permutation block of DES can be implemented as follows:

```

work pop 32 push 32 {

for (int i = 31; i >= 0; i--) {

push(peek(32 - P[i])); // P is the permutation array

}

for (int i = 0; i < 32; i++) {

pop();

}

}</pre>

```

First, the primitive names may confuse programmers since **push** and **pop** are commonly used for stacks, whereas each stream in stream programs has queue semantic. In addition, **push** and **pop** impose a specific ordering on reading input tokens and writing output tokens. This is why the first loop uses the reverse iteration order and why we need the second loop for book keeping.

In Elk, we use array notations to represent the current window of input and output tokens as follows:

(int[32] in) -> (int[32] out) {

for (int i = 0; i < 32; i++) {</pre>

```

out[31 - i] = in[32 - P[i]];

}

```

This description is more concise and closer to code that will be generated by an optimizing stream compiler; due to efficiency reasons or in order to preserve the atomic nature of each actor firing, the stream compiler will transfer tokens in bulk. In fact, an intermediate representation of a StreamIt compiler uses a form that is more similar to the Elk code shown above than to the StreamIt code. In short, StreamIt provides unnecessarily low-level primitives that help neither the programmer nor the compiler.

#### Basic Constructs of Elk:

Actor *Actor* is the building block of Elk. When an actor is fired, it invokes its *map* function, whose syntax is as follows:

```

actor Fir<int N> {

const int[N] coeffs; // member variable

Fir(const T[N] coeffs) { // constructor

this.coeffs= coeffs;

}

(int[N] in strides=1) -> (int[1] out) { // map function

int sum = 0;

for (int i = 0; i < N; i++) {

sum += coeffs[i]*in[i];

}

out[0] = sum;

}

}</pre>

```

The syntax of actor definition is similar to that of class definition in C++. An actor can have template parameters, member variables, constructors, and methods. One difference is that each actor actively executes its own code instead of being passively executed by threads as in C++ classes. In addition, each actor has one map function with special semantics: i.e., is invoked whenever an actor instance is fired.

The definition of map function starts with input and output streams that are denoted as arrays. The array notation associated with a stream represents the window of stream tokens that is accessed by the current actor firing. An input stream can have a stride attribute. Strides denote the amount of the window shift between consecutive actor firings. Within the map function, the syntax is identical to that of C++ except that an array for input stream cannot be written and an array for output stream cannot be read.

The number of tokens that are consumed or produced by an actor can be a variable. The code below shows an RLE (run length encoder) actor as an example.

```

actor Rle {

int count = 1;

(int[2] in stride=1) -> (int[] out) {

if (in[0] == in[1]) {

count++;

}

else {

out[0] = in[0];

out[1] = count; // Streams advance per actor invocation.

count = 1;

}

}

}

```

There are a few pre-defined actors such as RoundRobinSplitter, RoundRobinJoiner, and Duplicator, which are similar to the filters with the same names in StreamIt.

Several standard actors are also implemented as a library, which includes FileReader, FileWriter, Transpose, Buffer, Decimator, Adder, Summer, Subtractor, and Multiplier.

**Bundle** Elk provides a general composition construct, *bundle*, which allows arbitrary connections within. The syntax of bundle definition is identical to that of actor except that its map function describes actor or bundle connections instead of computation. The code below shows how we can build a band-pass filter using bundles:

```

bundle BandPassFilter<int N> {

int[N] hpfCoeffs, lpfCoeffs;

BandPassFilter(int lowFreq, int highFreq) {

computeHpfCoeffs(hpfCoeffs, lowFreq);

computeLpfCoeffs(lpfCoeffs, highFreq);

}

static void computeHpfCoeffs(int[N] coeffs, int cutoff) {

. . .

}

static void computeLpfCoeffs(int[N] coeffs, int cutoff) {

. . .

}

(int[] in) -> (int[] out) { // map function

in >> Fir<N>(hpfCoeffs) >> Fir<N>(lpfCoeffs) >> out;

}

}

bundle Main {

() -> () {

```

```

FileReader("in.dat") >>

BandPassFilter<32>(1000, 3000) >> FileWriter("out.dat");

}

```

In map functions of bundles, we connect actors or bundles through >> operator, which is adopted from the C++ I/O stream operator. Using >> operator, we can describe an arbitrary actor/bundle connectivity. For map functions in bundles, we can omit the size of arrays associated with input/output streams, which will be inferred by the compiler. The Main is a pre-defined bundle which is the entry point of the program.

We can instantiate multiple identical actors as follows:

```

// from dct.elk

in >> RoundRobinSplitter(8) >> IDCT8x8_1D_row_fast()*8 >>

RoundRobinJoiner(8) >> ...

```

We can also use if and for statements provided their conditional statements use compile-time constants as follows:

```

// from bitonic_sort.elk

for (int i = 0; i < numSeqP; i++) {

// numSeqP should be constant at the bundle invocation time.

if (1 > 2) { // 1 should be constant

tempIn[i] >> PartitionBitonicSequence(1, sortDir) >> tempOut[i];

// sortDir should be constant

}

else {

tempIn[i] >> CompareAndExchange(sortDir) >> tempOut[i];

}

}

tempOut >> RoundRobinJoiner(1) >> out;

```

**Stream** A *stream* represents data communication between actors. We can annotate a stream with a rate as shown below. The compiler exploits parallelism just enough to satisfy the real-time constraint associated with the rate instead of performing a best-effort parallelization, if a rate is specified as follows:

```

bundle Main {

() -> () {

stream<int> in rate=1MHz;

FileReader("in.dat") >> in >>

BandPassFilter<32>(1000, 3000) >> FileWriter("out.dat");

}

}

```

We can define an array of streams, which is useful in conjunction with **for** statements in a bundle:

```

// from bitonic_sort.elk

stream<int>[numSeqP] tempIn, tempOut;

for (int i = 0; i < numSeqP; i++) {

for (1 > 2) {

tempIn[i] >> PartitionBitonicSequence(1, sortDir) >> tempOut[i];

}

else {

tempIn[i] >> CompareAndExchange(sortDir) >> tempOut[i];

}

}

tempOut >> RoundRobinJoiner(1) >> out;

```

#### Elk High-level Compiler

**Output** C++ Code The Elk compiler (elmhc) is a source-to-source compiler. It generates C++ code that is designed to be architecture-independent. For each core, a separate C++ code is generated, and each of these separated codes has its own main

function. In the generated C++ code, architecture dependencies mainly come from how to express streaming (i.e., DMA) operations. We abstract these architecturedependent parts into two levels: concurrent queue library and intrinsic functions. Most of architecture-dependent parts can be expressed by our concurrent queue library interface, which is the higher level of the two abstractions.

#### **Compiler Structure and Important Phases**

**Front-end** We use the ANTLR parser generator [1] to parse .elk files and generate an abstract syntax tree (AST) of the whole program. Then, we generate a three address code (TAC) and a control flow graph for each actor as an intermediate representation.

#### **Important Phases**

- Bundle Flattening: We flatten the actor hierarchy that is expressed by the **bundle** construct in Elk. The **bundle** construct facilitates code reuse and modularization, but, during compilation, it is often more convenient to flatten the hierarchy.

- Constant Propagation: During the bundle flattening, we propagate constants through the hierarchy and within actor computation codes. In many occasions, we use Janino (an embedded Java compiler) [3] to fold a complex expression into a constant.

- Rate Analysis: We propagate real-time constraints associated with streams or actors by the **rate** construct. For example, if there is a low-pass filter actor followed by a high-pass filter actor, and the real-time constraint of the low-pass filter's input stream is 1KHz, we propagate the constraint to the high-pass filter and also set the real-time constraint of the high-pass filter to 1KHz (here, we assume that both low-pass and high-pass filter consume and produce 1 stream token per firing).

- Actor Computation Rate Estimation: We estimate the number of instructions per actor firing using a static analysis. We aggressively apply compiler optimizations such as conditional constant propagation [159], dead code elimination, and partial redundancy elimination [86] to our intermediate representation in order to consider optimizations that will be performed by the C++ compiler. When we encounter an if-else branch, we select the longest path. When we encounter a loop whose iteration count cannot be determined at compile-time, we mark the actor as a "dynamic" actor (to override this, the programmer can manually specify the computation rates of an actor). By the combination of results from the previous rate analysis phase and this phase, we can associate each actor with the computation requirement that is used in a later phase to satisfy the real-time constraints. For example, if the propagated rate for a DCT actor is 1KHz, and if the estimated actor computation rate is 400Hz, the computation requirement for the DCT actor is 2.5 cores.